type

Post

status

Published

date

Sep 27, 2024

slug

ZYNQ

summary

tags

FPGA

category

FPGA

icon

password

上次编辑时间

May 18, 2025 12:43 PM

AI summary

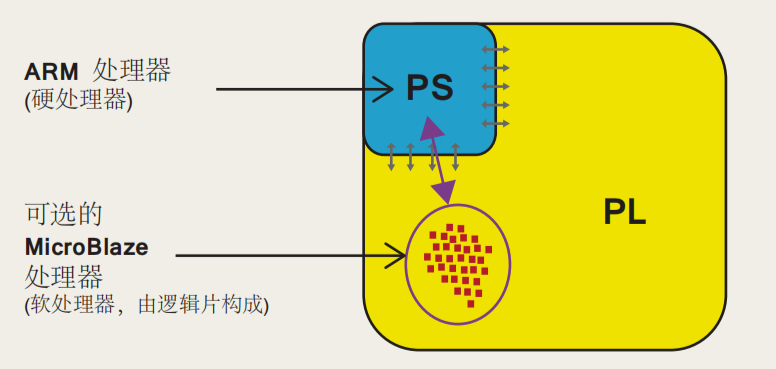

ZYNQ 体系结构

Zynq 的总体架构包含两个部分:PS(处理器系统)和 PL(可编程逻辑)。这两部分的供电电路上相互独立的,因此 PS 和 PL 可以单独使用,不被使用的部分可以断电以降低功耗。不过 Zynq 最有价值的模式上两个组成部分结合起来使用。

PS(处理器系统)

作为处理器系统的基础,所有芯片都包含一颗双核的 ARM Cortex- A 9 芯片。这是一颗硬处理器,是芯片上专门且优化过的硅片元件。

除了“硬”处理器,还有另外一种方案,像是 MicroBlaze 这样的“软”处理器,这是由 PL 端端单元组合成的,即和 PL 端的 IP 是等价的。相比之下,“硬”处理器可以获得相对较高的性能,“软”处理器的数量和精确实现是灵活的。

值得一提的是,可以在 zynq 的 PL 端分配一个或多个 MicroBlaze 软处理器,用于和硬核协同工作。比如可以让软核负责协调特定的底层功能和系统之间的配合,将要求不高的任务从硬核上脱离出来,提高整体性能。

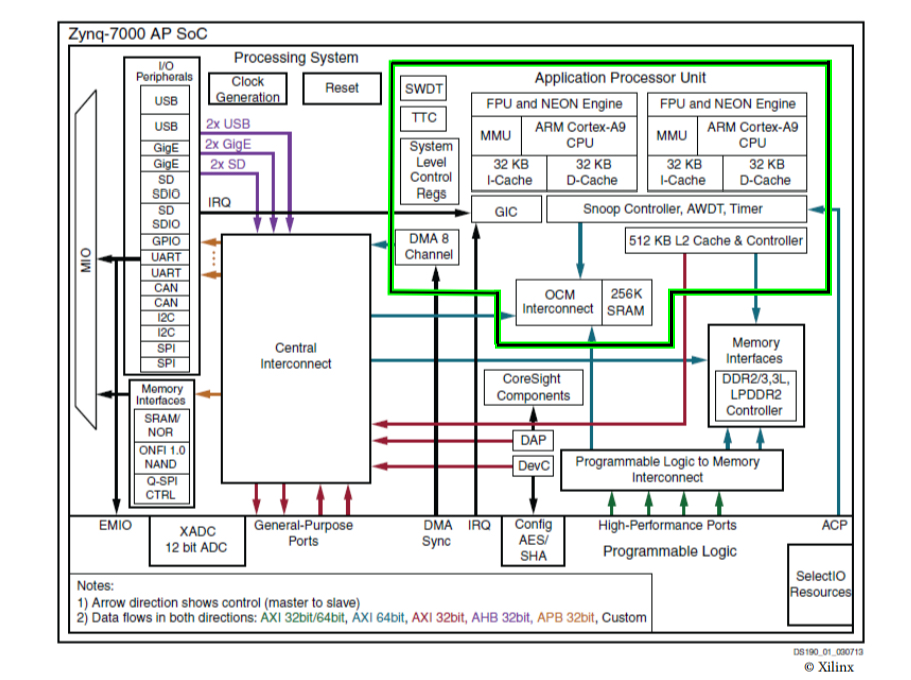

Zynq 的 PS 端里面并非只有 ARM 处理器,还有一组相关的处理资源,构成一个应用处理器单元(Application Processing Uint,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路。

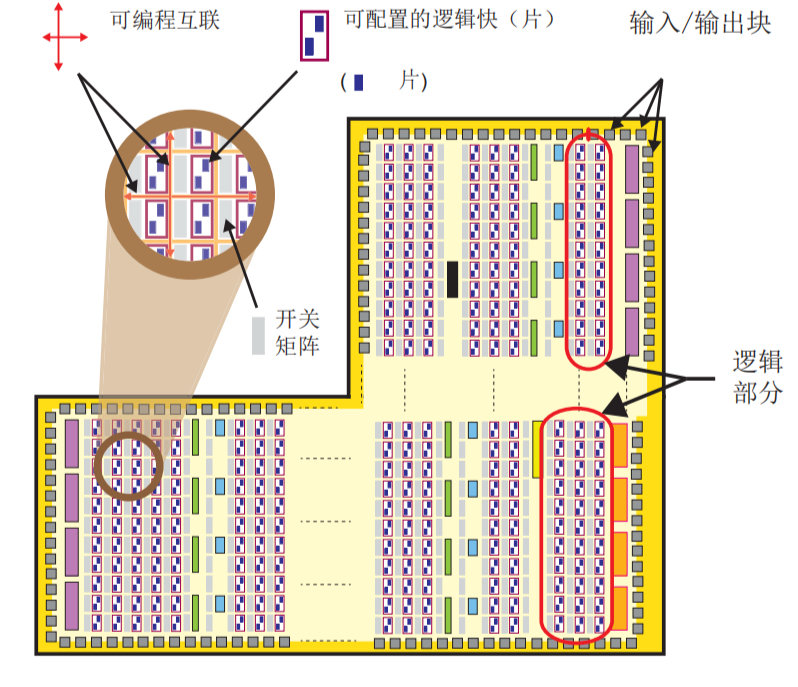

PL(可编程逻辑)

Zynq 中的逻辑部分是基于 Artix 7 和 Kintex 7 的 fpga 组件。

逻辑部分

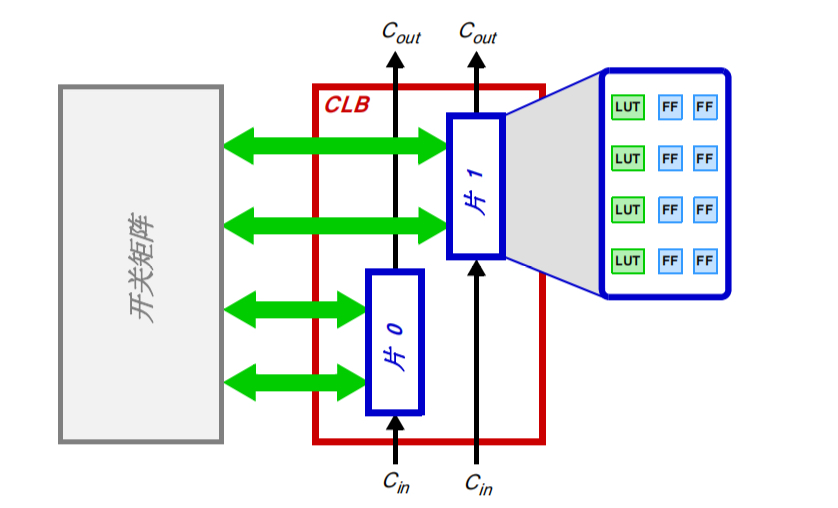

- 可配置逻辑块(CLB)—— CLB 是逻辑单元的小规模、普通编组,在 PL 中排列为一个二维阵列,通过可编程互联连接到其他类似的资源。每个 CLB 内都含有两个逻辑片,并紧邻一个开关矩阵。

- 片(Slice)—— CLB 里的子单元,里面有实现组合和时序逻辑电路的资源。

- 查找表(Lookup Table,LUT)—— 一个灵活的资源,可以实现

- 至多 6 个输入的逻辑函数

- 一小片只读存储器(ROM)

- 一小片随机访问存储器(RAM)

- 一个移位寄存器

LUT 可以按需组合形成一个更大的逻辑函数、存储器或移位寄存器。

- 触发器(Flip-flop,FF)—— 一个实现一位寄存的时序电路,带有复位功能。其中一个用处是实现锁存。

- 开关矩阵(Switch Matrix)—— 每个 CLB 旁边都有一个开关矩阵,实现灵活的布线功能来连接 CLB 内的单元,或把 CLB 与 PL 内的其他资源连接起来。

- 进位逻辑(Carry Logic)—— 算术电路需要在相邻的片之间传递信号,这就是通过进位逻辑来实现的。

- 输入/输出块(IOB)—— IOB 实现了 PL 逻辑资源之间的对接,并提供物理设备“焊盘”来连接外部电路。每个 IOB 可以处理一位的输入或输出信号,IOB 一般位于芯片的周边。

特殊资源:DSP 48 E 1 和 BRAM

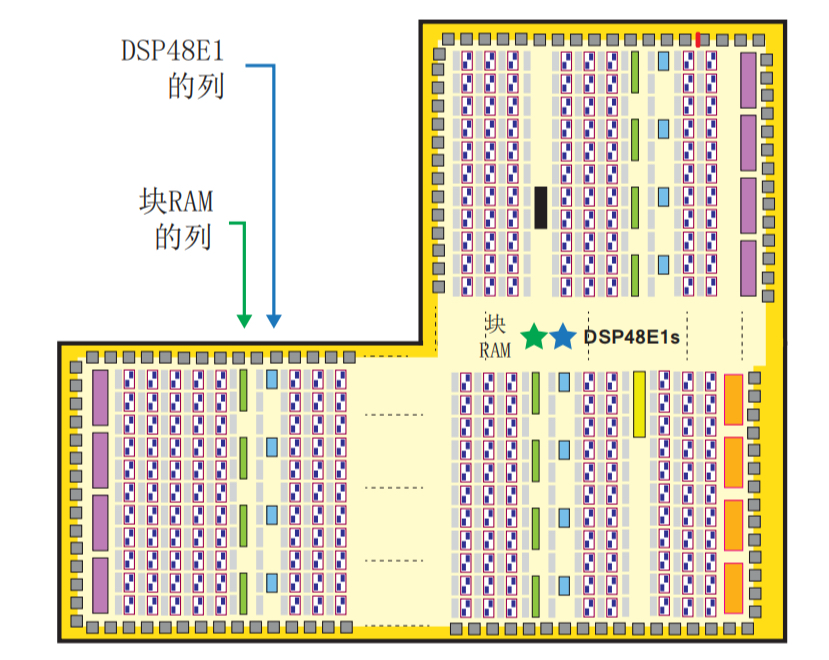

这两个资源都按列排列集成在逻辑阵列中,嵌入在逻辑部分中,而且彼此靠近,原因是密集计算和给内存中存储数据往往是紧密联系的运算。

BRAM

Zynq-7000 的 BRAM 和其他 Xilinx 7 系列 FPGA 里的 BRAM 是相同的,都可以实现 RAM、ROM、FIFO,同时还支持纠错编码。

每个 BRAM 里最多可以存储 36 KB 的信息,可以被配置为一个 36 KB 的 RAM 或者两个独立的 18 KB 的 RAM。还可以被“重塑”来包含更多的更小的单元,或者组合起来组成更大容量大 RAM。

使用 BRAM 意味着能在芯片内部优化的专用存储单元内,用很小的物理空间存储大量的数据。另一种方法是分布式 RAM(Distributed RAM),DRAM 是用逻辑部分里的 LUT 来搭建的,想要构成和 BRAM 大小相当的的存储器,需要用到大量的 LUT,而且实现的结果还受到剧增的逻辑和布线延迟所造成的时序性能受限的影响。另一方面,用 DRAM 实现小存储器是有优势的,这样资源利用率高,并且布局更灵活。BRAM 往往能工作在芯片支持的最高时钟频率下。

DSP 48 E 1

逻辑部分的 LUT 可以用来实现任意长度的算术运算,但由于长字长的算术电路会在逻辑片内占据较大的空间,这样的布局和布线会导致时钟频率是次优的,因此最好拿 LUT 做短字长的运算。

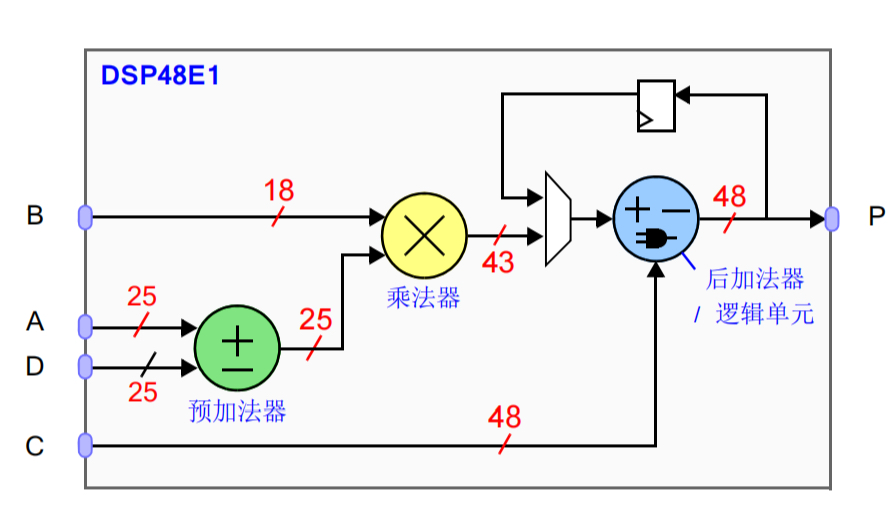

DSP 48 E 1 是专门用于实现对长字长信号的高速算术运算的逻辑片,是专用的硅片资源,并且在逻辑单元内部包含了预加法器/减法器、乘法器和后加法器/减法器。

后加法器还可以用作逻辑单元,此时它可以做逻辑运算,支持所有的基础布尔运算。

如果需要更大字长的运算,可以将多个 DSP 组合起来做扩展。

通用输入/输出

Zynq 上的通用输入/输出功能合起来被成为 SelectIO 资源,它们被组成 50 个 IOB 一组,每个 IOB 都有一个焊盘,与外部世界连接。

I/O 组分为高性能(High Preformance,HP)或高范围(High Range,HR)。HP 接口的电压最高为 1.8 V,通常用作连接存储器和其他芯片的高速接口;HR 接口允许 3.3 V 的电压,适合做各种 IO 标准的连接。两种接口都支持单端和差分信号。

每个 IOB 还包含一个 IOSERDES 资源,可以做并行和串行的可编程转换,数据位宽是 2~8 位。

通信接口

Zynq 内部含有嵌入在逻辑部分里的 GTX 收发器和高速通信接口块。

其他可编程逻辑扩展接口

- ADC—— XADC,具有两个独立的 12 位 ADC,每个采样率为 1 Msps。

- 时钟—— PL 接收来自 PS 的四个独立的时钟输入,另外还能产生和分发它自己的与 PS 无关的时钟。

- JTAG 调试接口

PS 与 PL 之间的接口

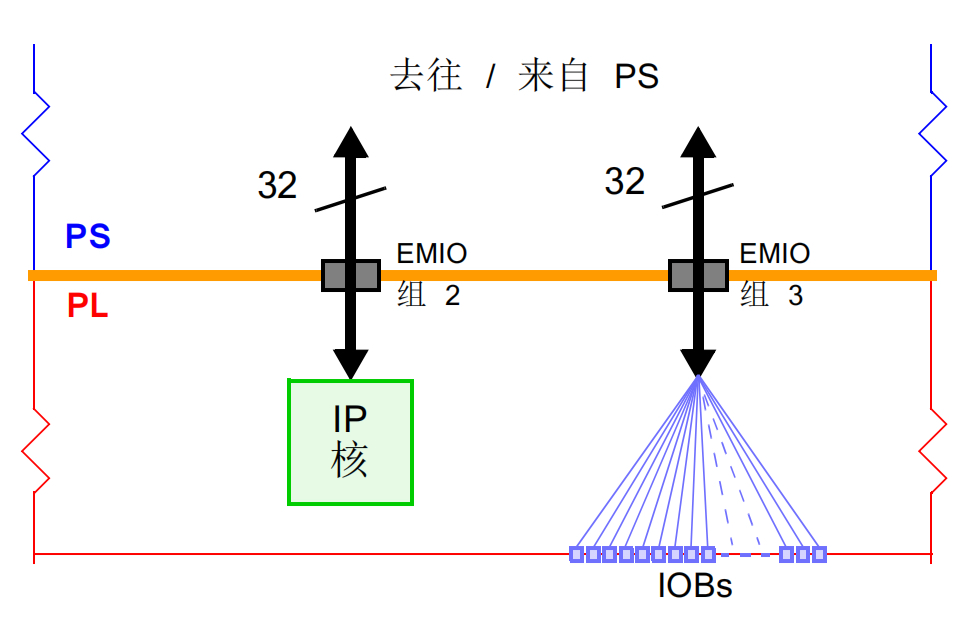

如前所述,Zynq 的表现不仅仅依赖于它的两个组成部分 PS 和 PL 的特性,还在于能把两者协同起来形成完整、集成的系统的能力。这其中起关键作用的,是一组高度定制的 AXI 互联和接口用来在两个部分之间形成桥梁。另外,在 PS 和 PL 之间还有一些其他类型的连接,特别是 EMIO。

AXI

高级可扩展接口(Advanced eXtensible Interface)。当前版本为第四代 AXI 4 。

AXI 4

用于存储映射连接,支持最高的性能,通过一簇高达 256 个数据字的传输来给定一个地址。

AXI 4-Lite

简化的连接,只支持每次传输一个数据。AXI 4 Lite 也是存储映射的,每次传输一个地址和单个数据。

AXI 4-Stream

用于高速流式数据,支持批量传输无线大小的数据。没有地址机制,适合源与目的之间的直接数据流。

EMIO 接口

EMIO 涉及两个域之间的传输,是由一组简单的导线连接实现的。

EBAZ 4205 矿板资料汇总

扩展版

开发板补全

原理图相关

矿板原理图

PCB